Lin MP, Hsu C, Chang Y (2011) Recent research in clock power saving with multi-bit flip-flops. In: IEEE transactions on very large scale integration (VLSI) systems, vol 21, no 4, pp 624–635, Shyu Y, Lin J, Huang C, Lin C, Lin Y, Chang S (2013) Effective and efficient approach for power reduction by using multi-bit flip-flops. In: Green circuits and systems (ICGCS) international conference Yan J-T, Chen Z-W (2010) Construction of constrained multi-bit flip-flops for clock power reduction. In: 2010 International conference on computer application and system modeling (ICCASM 2010), pp V15-526–V15-529,

Liang W, Long J (2010) A cryptographic algorithm based on Linear Feedback Shift Register. Shiny MI, Devi N, LFSR based secured scan design testability techniques. In: 2018 second international conference on intelligent computing and control systems (ICICCS), pp 1979-1984, Kumar GS, Saminadan V (2018) Low power LFSR for BIST applications. ISSN: 2250-3498Īhmad A, Al-Abri D (2010) Design of an optimal test simulator for built-in self test environment. Ponnusamy S (2014) Clock power reduction using multi-bit flip-flop technique. Reddy K, Jaya R, Madhav Rao S (2013) Power optimized multi-bit flip-flops using gated driver tree.

Mittal P, Shah D (2020) Linear feedback shift register-based test pattern generators - a comparative study. Int J Res Anal Rev 11Ĭheng Y (2007) Design of low-power double edge-triggered flip-flop circuit, 2054-2057. Madhu Shakya SA (2018) Design low power CMOS D-flip flop. In: 2015 4th International Conference on Reliability, Infocom Technologies and Optimization (ICRITO) (trends and future directions), pp 1–6, Kumar H, Kumar A, Islam A (2015) Comparative analysis of D flip-flops in terms of delay and its variability. The chip area is also reduced as it uses only four multibit flipflops in place of an eight D flipflop in the proposed design. The result analysis provides that the power of standard eight-bit LFSR is about 92,732.236 nW, and it is reduced to 35,217.804 nW as we use multibit flipflops to implement an eight-bit LFSR.

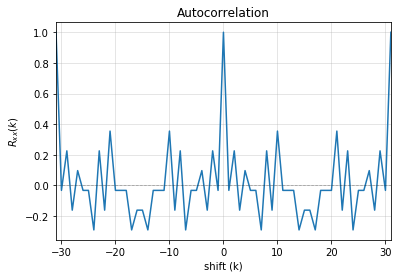

The synthesis and physical design are carried out using Cadence Genus and Innovus tools. The proposed design simulation is done using the Xilinx IDE. The total design area is reduced due to the usage of the multibit flipflop without affecting the performance of the design. Multibit flipflop is used in applications where low power and area is the main concern. The proposed technique uses multibit flipflops for designing the LFSR. The standard implementation of LFSR uses D flipflops and exclusive OR connected linearly. The Linear Feedback Shift Register (LFSR) can be employed to generate pseudorandom patterns in test generators. In the emerging world of VLSI technologies, the challenges for the VLSI designers keep raising to produce circuits that consume low power, area and speed.

0 kommentar(er)

0 kommentar(er)